|

|

ENCICLOPEDIA DELLA RADIOELETTRONICA ED ELETTRICA Chip di memoria di STMICROELECTRONICS. Dati di riferimento

Enciclopedia della radioelettronica e dell'elettrotecnica / Applicazione dei microcircuiti L'articolo fornisce una panoramica dei vari tipi di memoria sviluppati e prodotti da STMicroelectronics, uno dei principali produttori mondiali di componenti elettronici, inclusi i chip di memoria, e che dispone di una tecnologia unica per la produzione di memorie Flash e sistemi di memoria programmabile su un singolo patata fritta. Attualmente, STMicroelectronics (ST) sviluppa e produce commercialmente i seguenti tipi di chip di memoria: EPROM - memoria con cancellazione ultravioletta e programmazione una tantum, inclusi chip di memoria standard come OTP и UV EPROM chip di memoria avanzati OTP и UV EPROM famiglia Tigre Gamma, chip di una nuova famiglia di memoria ROM flessibile, progettato per sostituire MaskROM, così come i chip di memoria BALLO DI FINE ANNO и RPM WSI (USA), entrata a far parte della ST; EEPROM и SERIAL NVM (memoria seriale non volatile a lungo termine) - i chip di memoria sono prodotti da memoria non volatile riprogrammabile seriale EEPROM con diversa interfaccia bus, chip seriali Cromatografia -memoria, chip di memoria standard per scopi speciali (ASM) e senza contatto (SENZA CONTATTO RICORDI) chip di memoria; Tipo di memoria flash NOR - ST produce chip di memoria Flash: standard di settore con diversi alimentatori, con architettura estesa per varie applicazioni, chip di memoria eterogenei e chip di memoria Flash della famiglia " Lampo di luce "; Tipo di memoria flash NAND - una nuova direzione nella produzione dei chip di memoria ST. SRAM - La società ST produce chip di memoria SRAM asincroni a bassa potenza con alimentazione e velocità diverse; NVRAM - Esistono diverse soluzioni per SRAM con batteria tampone, che si classificano in Supervisori, Zeropower, Timekeeper e Serial Real Time Clock (Serial RTC); PSM - in linea con la direzione strategica dei "sistemi su chip", la ST progetta e produce chip di memoria programmabili che forniscono una soluzione di sistema di memoria completa per lo sviluppo di microcontrollori e processori di segnale (DSP); Smart card - è disponibile un'ampia gamma di chip per Smartcard e sistemi di sicurezza. Un gran numero di tipi e tipi di chip di memoria prodotti da ST non consente la loro copertura dettagliata anche nell'ambito di un articolo di revisione. Pertanto, qui cercheremo di soffermarci solo sulle caratteristiche principali di alcune famiglie di chip di memoria ST tra quelle mostrate in Fig. uno.

ST è uno dei principali produttori di memorie al mondo. OTP и EPROM con cancellazione UV, utile per progettare, produrre e sostituire le ROM delle maschere perché programmate a fine produzione. I microcircuiti prodotti hanno una capacità da 64 kbps a 64 Mbps con un'alimentazione di 5 e 3 V, velocità sufficiente, vari pacchetti, compresi quelli per montaggio a parete. L'organizzazione della memoria del dispositivo può essere di tipo x 8, x 16 e x 8 / x 16. Decifrazione delle denominazioni dei chip di memoria ST della forma OTP и UV EPROM mostrato in Fig. 2. Il portafoglio di prodotti comprende circuiti integrati standard da 5 V e 3,3 V, circuiti integrati avanzati della famiglia Tigre Escursione con alimentazione 3 V (2,7-3,6 V) e microcircuiti di nuova famiglia FlessibileROM™. Questi tipi di memoria sono disponibili in package FDIP con finestra in ceramica e in plastica PDIP a doppia fila, nonché in package PLCC e TSOP a montaggio superficiale. Per serie a bassa tensione Tigre Escursione ST ha utilizzato la tecnologia più recente OTP e UV EPROM. I miglioramenti strutturali legati allo spessore degli strati di base hanno permesso di migliorare sensibilmente le prestazioni elettriche. Una riduzione del 25% dello spessore dello strato di ossido di gate ha permesso di abbassare la tensione di soglia della cella e aumentare la frequenza di campionamento quando alimentata a 2,7 V. STMicroelectronics si impegna a fornire al consumatore nuovi prodotti con caratteristiche elettriche migliorate e pertanto raccomanda ai clienti di sostituire la serie "V" con alimentazione da 3 - 3,6 V con la serie "W" - Tigre Gamma, che ha le migliori prestazioni se alimentato da 2,7 - 3,6 V. Parametri di temporizzazione per la serie Tigre Escursione garantito dal doppio test dei chip a 2,7 V e 3 V. Il tempo di accesso a 2,7 V è segnato sul chip e il tempo di accesso più veloce è specificato nella descrizione. I tempi di accesso per tensioni di alimentazione superiori a 2,7 V sono operativi. famiglia UV e OTP EPROM Tigre Escursione caratterizzato da bassissimi consumi, elevata velocità di funzionamento e allo stesso tempo rapido accesso con brevi tempi di programmazione. Il tempo di programmazione del chip è lo stesso sia per le modalità di programmazione a parola che a byte. Per i chip più recenti con una densità di 4 MB e 8 MB, la velocità di programmazione è stata aumentata a 50 µs per parola o byte. Microcircuiti della serie a bassa tensione Tigre Escursione completamente pin compatibile con la serie standard 5V UV и OTP EPROM . Ciò garantisce che siano completamente compatibili per le applicazioni in cui la potenza del microprocessore viene modificata da 5 V a 3 V.

La tecnologia EPROM di ST viene costantemente migliorata. Nuove prospettive si aprono con l'introduzione di una nuova architettura di chip di memoria basata sull'uso della tecnologia delle celle di memoria multi-bit per ottenere densità di registrazione elevate, a partire da una capacità di 64 M bit. Inoltre, ogni nuovo sviluppo contiene diverse innovazioni fotolitografiche che migliorano le prestazioni elettriche dei microcircuiti. Con l'ingresso in STMicroelectronics di WAFERSCALE INC (USA), la possibilità di fornire chip di memoria del tipo BALLO DI FINE ANNO (ROM programmabile) / RPM (ROM riprogrammabile). Questi circuiti integrati sono disponibili in tre intervalli di temperatura operativa: commerciale (da 0 a +70°C), industriale (da -40 a +85°C) e militare (da -55 a +125°C). Inoltre, alcuni componenti sono fabbricati secondo lo standard militare (SMD), inclusa la EPROM. L'ultimo sviluppo di STMicroelectronics nel campo delle ROM programmabili elettricamente è una famiglia di FlessibileROM™, che può essere utilizzato come semplice sostituto di qualsiasi ROM. Questa famiglia programmabile una tantum, prodotta utilizzando la tecnologia da 0.15 µm della ST, è disponibile per il consumatore con una capacità di memoria iniziale di 16 M bit. La nuova famiglia di chip di memoria "FlexibleROM" si riferisce al tipo di memoria non volatile ed è progettata per memorizzare il codice del programma. "FlexibleROM" - ideale per l'uso al posto della maschera ROM (MaskROM) e il passaggio dalla memoria Flash alla ROM dopo il debug del programma, se non si prevede di modificare il codice del programma in futuro. Grazie alla tecnologia basata su Flash, anche i tempi di programmazione sono notevolmente ridotti. Le FlexibleROM sono dotate di una capacità di programma dettagliata generica ad alta velocità di trasmissione dati, che consente di programmare un dispositivo a 64 M bit in soli nove secondi. Un altro vantaggio rispetto ad altre ROM One-Time-Program è l'elevata velocità di programmazione, poiché il 100% della funzionalità dell'array di memoria viene verificato durante il test. I chip di memoria FlexibleROM utilizzano una tensione di alimentazione da 2,7 V a 3,6 V per le operazioni di lettura e da 11,4 V a 12,6 V per la programmazione. I dispositivi hanno un'organizzazione a 16 bit, per impostazione predefinita, all'accensione, la modalità di memoria è impostata su "Leggi", in modo che possano essere letti come ROM (ROM) o EPROM (EPROM). Memoria seriale non volatile - il tipo più flessibile di memoria non volatile non volatile, che offre la possibilità di scrivere a livello di byte, senza la necessità di cancellare i dati prima di scrivere un nuovo valore. Questo li rende ideali per la memorizzazione dei parametri. Le famiglie di memorie flash seriali della ST hanno funzionalità di "cancellazione settore/lampeggio pagina" e "cancellazione pagina/lampeggio pagina". Ciò è possibile grazie alla maggiore granularità della memoria rispetto alla memoria Flash standard, che ha una caratteristica di granulosità che non corrisponde alla caratteristica a livello di byte della EEPROM seriale. La ST ha una ricca esperienza nell'utilizzo di chip di memoria seriali negli elettrodomestici. Occupa una posizione leader nella produzione di chip di memoria per l'elettronica automobilistica, nonché per il mercato dei componenti per computer e delle periferiche. Queste aree sono i principali consumatori di chip di memoria a lungo termine. Quest'anno per EEPROM l'azienda utilizza una tecnologia di produzione da 0.35 micron, che ha permesso di portare la capacità di memoria fino a 1 Mbit in linea con le esigenze del mercato. Allo stesso tempo, la tecnologia di produzione della memoria flash seriale ha raggiunto il livello di 0.18 µm, ed è diventato possibile produrre questo tipo di memoria completamente in accordo con le richieste del mercato. Il portafoglio NVRAM seriale ST include una gamma di circuiti da 256 bit a 16 Mbit. Tutti i chip di memoria ST sono forniti con descrizioni, esempi applicativi e file modello, che li rendono facili da usare. I chip di memoria non volatile seriali ST sono disponibili in cinque gamme di tensione: da 4,5 V a 5,5 V, da 2,5 V a 5,5 V, da 2,7 V a 3,6 V, da 1,8 V a 5,5 V e da 1,8 V a 3,6 V. EEPROM di durata del design: più di un milione di cicli di riscrittura con sicurezza dei dati per oltre 40 anni. I chip sono prodotti in vari pacchetti, inclusi i tradizionali tipi PSDIP, TSSOP, SO, nonché i moderni tipi LGA e SBGA (film sottile). Inoltre, è possibile fornire trucioli in confezioni su tamburo e in forma non segata. La ST Microelectronics produce un'ampia gamma di memorie seriali di alta qualità eeprom, con densità da 1 kb a 1 Mb, con tre bus seriali standard del settore (400 kHz, I? C, bus a 2 fili con una densità fino a 1 M bit, tipo di bus veloce da 1 M Hz MICROFILO (r) con una densità da 1 kbps a 16 kbps e un bus SPI ultraveloce a 10 MHz con una densità fino a 256 kbps), con un'alimentazione di 5 V, 2,5 V e 1,8 V. Viene mostrata la notazione EEPROM seriale per i pacchetti tipici nella Figura 3. Per piastre non segate e microcircuiti nei tamburi, le designazioni possono differire leggermente.

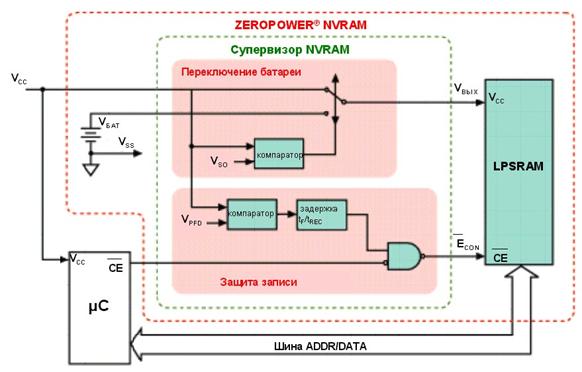

microchip coerente EEPROM con bus I2C consigliato per utilizzare in applicazioni che non richiedono un'elevata velocità del bus per l'accumulo e l'archiviazione dei dati, ma che desiderano essere in grado di leggere/scrivere byte per byte e pagina per byte. Il bus funziona a 400 kHz con tensioni di alimentazione fino a 1,8 V. La EEPROM seriale della ST è disponibile in una varietà di contenitori: DIP in plastica dual-in-line, SO, MSOP, montaggio superficiale TSSOP e ball array SBGA. Chip di memoria EEPROM con bus SPI preferito per applicazioni bus ad alta velocità. Con l'avvento dei chip con velocità da 5 MHz a 10 MHz e capacità da 512 kbps a 1 Mbps, questo bus sta rapidamente guadagnando popolarità nel mercato dei chip di memoria. Sono presenti EEPROM con bus SPI HOLD ("Capture"), che consente di mantenere la sincronizzazione durante le pause nel processo di trasmissione di sequenze di dati sul bus. Inoltre, c'è uno speciale ingresso di controllo W per proteggere la matrice di memoria dalla scrittura. Chip di memoria EEPROM con bus MICROFILO® disponibile con capacità da 256 bit a 16 kbit. Attualmente, il bus MICROWIRE è ampiamente utilizzato in molti dispositivi moderni che richiedono una velocità di trasferimento dati sufficientemente elevata senza l'uso di bus di indirizzi/dati esterni. La famiglia ST di chip di memoria flash seriali ad alta velocità e bassa tensione dispone di un'interfaccia compatibile con SPI a quattro fili, che consente di utilizzare la memoria flash al posto della EEPROM seriale. Realizzati utilizzando la tecnologia CMOS Flash altamente durevole, questi chip forniscono almeno 10000 cicli di riprogrammazione per settore con oltre 20 anni di conservazione dei dati. Attualmente esistono due sottofamiglie complementari di memoria flash sequenziale con capacità di cancellazione di settori o pagine: Serial Erase Flash con programmazione pagina: serie M 25 Pxx (completamente in produzione) Memoria Flash Seriale con Cancellazione Pagina e Programmazione: Serie M 45 PExx (questa è una nuova serie, campioni disponibili, piena produzione in corso). Quando si esaminano diversi tipi di chip di memoria non volatile seriale ad alta densità, l'M25Pxx a 25 MHz è significativamente più veloce di molti altri tipi di chip di memoria flash seriale. La famiglia ST Serial Flash può caricare 1 MB di RAM in 43 ms con un numero minimo di istruzioni, rendendole facili da usare. Le protezioni tecniche e software proteggono le informazioni archiviate dalla sovrascrittura. Per ridurre il consumo energetico, questi circuiti integrati funzionano con una singola alimentazione da 2,7 V a 3,6 V e hanno una modalità a basso consumo che consuma meno di 1 µA di corrente. Inoltre, l'interfaccia a quattro fili riduce notevolmente il numero di pin del dispositivo utilizzati per controllare la comunicazione bus, con conseguente elevata integrazione e costi inferiori rispetto ad altri circuiti simili. I chip di memoria della serie M25Pxx sono disponibili in contenitori S08, LGA e MLP larghi e stretti. Per valutazione e programmazione L'M 25 PXX dispone di un pratico programmatore/lettore. Questo programmatore si collega direttamente a un PC e fornisce all'utente l'accesso diretto e il controllo della memoria flash seriale M 25 xxx in qualsiasi configurazione. M45PExx è una serie di chip di memoria non volatile ad alte prestazioni con una granulometria maggiore rispetto a prima. Qualsiasi pagina di 256 byte può essere cancellata e programmata individualmente e il comando Write prevede la possibilità di modificare i dati a livello di byte. Inoltre, l'architettura dell'M45PExx è ottimizzata per ridurre al minimo il software applicativo richiesto. Occorrono 256 ms per scrivere, 12 ms per programmare o 2 ms per cancellare per modificare una pagina di 10 byte. Ciò rende i chip di memoria non volatile seriale ad alte prestazioni M45PExx molto adatti per l'uso in applicazioni che richiedono l'archiviazione di grandi quantità di dati che cambiano frequentemente. I chip di memoria specializzati sono personalizzati per applicazioni specifiche o progettati per soddisfare requisiti specifici. Si basano su array di memoria standard con circuiti I/O specifici e logica interna specializzata. Questi prodotti sono basati su EEPROM seriale e includono la logica per applicazioni come monitor per computer "Plug and Play" con standard VESA, moduli DRAM per computer, ecc. Tra questi microcircuiti, si può notare M 24164-16 Kb in cascata EEPROM con indirizzamento speciale, possibilità di utilizzare 8 dispositivi in cascata su un bus e indirizzamento speciale utilizzato in caso di conflitto sul bus I 2 C. Un altro chip specializzato che può essere ampiamente utilizzato nel nostro mercato è M 34 C 00 - descrittore scheda elettronica, progettato per memorizzare piccole note elettroniche sulla lavagna . L'M34C00 può salvare il numero di registrazione, le impostazioni di fabbrica (default), le impostazioni utente, i dati sugli eventi durante la vita della scheda, le informazioni sui guasti e la manutenzione di servizio di qualsiasi scheda, ecc. Questo chip ha 3 banchi di 128 bit (uno è non cancellabile (tipo OTP), un banco EEPROM standard e un banco EEPROM standard con capacità di protezione da scrittura permanente), I ? Interfaccia seriale bus C, alimentazione da 2,5 V a 5,5 V, custodia SO 8 o TSSOP 8, temperatura di esercizio - 40 … + 85°C. Chip di memoria senza contatto sono un prodotto specifico Secondo la loro classificazione, da un lato, possono essere attribuiti a EEPROM specializzate e, dall'altro, possono essere distinti come un tipo di memoria indipendente, recentemente ampiamente utilizzato in vari campi. ST ha contribuito allo sviluppo di un nuovo standard ISO per la memoria di comunicazione contactless - ISO 14443 tipo B (implementato nei dispositivi a microcontrollore su Smartcard nei trasporti e molte altre applicazioni), nonché ISO 15693 e ISO 18000. La ST offre ora una nuova serie di chip di memoria senza contatto e chip di comunicazione RF senza contatto per applicazioni quali tag, identificazione a radiofrequenza (RFID) e sistemi di accesso senza contatto che utilizzano chip di memoria dedicati. Notiamo le caratteristiche di alcuni microcircuiti di questo tipo diffusi sul mercato russo. chip SRIX 4 K ha 4096 bit utente EEPROM con OTP, contatore binario e protezione da scrittura. Conforme alla norma ISO 14443-2/3 tipo B. Possiede la funzione anti-clonazione brevettata da France Telecom. Funziona su una frequenza portante di 13,56 M Hz con una frequenza sottoportante di 847 kHz, una frequenza con una velocità dati di 106 kbps. Utilizza la modulazione di ampiezza (ASK) per la trasmissione dei dati dal lettore alla carta e la modulazione di fase binaria (BPSK) per la trasmissione dalla carta al lettore. chip LR 512 dispone di 512 bit con blocco a livello di blocco dati. È pienamente conforme ai requisiti ISO 15693 (fino a 1 metro) e E. UN. S. Funziona a una frequenza portante di 13,56 MHz con codifica a impulsi 1/4 e 1/256 a velocità dati alte e basse su una o due frequenze di sottoportante. La modulazione dell'ampiezza dei dati viene eseguita durante la trasmissione dal lettore alla tessera e la codifica Manchester durante la trasmissione dalla tessera al lettore. In un microchip CRX14 è presente un meccanismo di comunicazione radio su chip con protocollo ISO 14443 tipo B e modulazione (interfaccia radio). Ha la funzione anti-clonazione brevettata da France Telecom. Fornisce l'accesso seriale alla base a 400 kHz su un bus seriale a due fili I ? C con connettività bus singolo a otto CRX 14. Ha un buffer di 32 byte per i pacchetti di input e output e un calcolatore CRC integrato. Prodotto in astuccio S 016 Stretto (compresso). ST è una delle poche aziende che sviluppa e produce chip RAM non volatili (NVRAM). La soluzione della ST per garantire la sicurezza dei dati della RAM durante i guasti e la perdita di alimentazione esterna consiste nell'utilizzare un'alimentazione di backup (batteria al litio in miniatura) posizionata direttamente sopra il chip o sulla scheda madre. Sulla base di attività basate su RAM, la ST produce quattro tipi di chip NVRAM: supervisori, ZEROPOWER® NVRAM, Serial RTC e TIMEKEEPER® NVRAM. Esistono due classi di supervisori: supervisori a microprocessore (Microprocessore supervisore) e supervisori ROM non volatili (NVRAM supervisore), ed è anche possibile una combinazione di entrambe le classi. Le funzioni principali del supervisore a microprocessore (µ P) sono il monitoraggio della tensione e la funzione watchdog. La maggior parte dei supervisori a microprocessore include queste funzionalità. Nei microcircuiti combinati è possibile anche l'integrazione di altre funzioni. Le funzioni principali del supervisore NVRAM sono il monitoraggio della tensione con commutazione della batteria e protezione da scrittura. Il monitor di tensione protegge il microprocessore (e il sistema) monitorando la tensione di alimentazione e generando un segnale RIPRISTINA (RIPRISTINA) per il passaggio del microprocessore allo stato iniziale ad un valore inaccettabilmente basso della tensione di alimentazione. Questa opzione è chiamata Basso Tensione Individuare (LVD) - "Rilevamento di bassa tensione". All'accensione, il monitor di tensione emette anche un segnale di RESET fino a quando la tensione di alimentazione non si è stabilizzata. Questa opzione è chiamata Energia - on Reset (por) - "Reset all'accensione". Un circuito di commutazione della batteria di emergenza integrato monitora la tensione dell'alimentatore esterno. Quando scende al di sotto di una certa soglia di commutazione, si verifica un passaggio all'alimentazione a batteria, che fornisce un'alimentazione di tensione continua alla RAM statica a basso consumo (LPSRAM) per memorizzare i dati al suo interno. Un circuito di protezione da scrittura integrato controlla la tensione dell'alimentatore esterno e, quando scende al di sotto di un certo livello di soglia, chiude l'accesso a LPSRAM. A volte, per ottenere RAM non volatile, gli sviluppatori risolvono il problema di crearli invece di utilizzare i moduli disponibili. La RAM standard a bassa potenza (SRAM) può essere convertita in NVRAM aggiungendo una batteria, un circuito di protezione da scrittura e un circuito di commutazione della batteria. ST dispone di diversi dispositivi che integrano tutte queste funzionalità. Inoltre, la batteria e il cristallo sono integrati in un pacchetto SNAPHAT ®, che semplifica il compito di sviluppare una soluzione NVRAM. Poiché l'orologio in tempo reale necessita di un interruttore della batteria e di un circuito di protezione da scrittura per alimentare l'orologio in tempo reale, è naturale desiderare di avere l'orologio in tempo reale nel supervisore NVRAM. ST ha tre chip che hanno questa combinazione: questi sono chip M41ST85, M48T201 и M48T212 . Tutti e tre questi dispositivi includono anche funzioni di supervisione del microprocessore: POR, LVD e watchdog. I supervisori NVRAM con un orologio in tempo reale sono chiamati "TIMEKEEPER® Supervisor. Uno degli ultimi sviluppi della ST è un chip M41ST87 nella custodia SOX28 progettata per l'uso nei registratori di cassa. Questo supervisore è progettato specificamente per applicazioni che richiedono un elevato grado di protezione e sicurezza dei dati. Microcircuiti M41ST87 combinato con schemi di rilevamento e cancellazione di manomissioni all'interno del supervisore per proteggere dispositivi remoti come terminali POS e carte di credito. Integrano il supervisore NVRAM, l'orologio seriale in tempo reale e il supervisore del microprocessore in un nuovo package ST SOIC (SOX28) a 28 pin. Oltre al cristallo, la confezione di SOX28 contiene anche quarzo a 32 kHz, che ha ridotto il profilo e le dimensioni dell'area di contatto del microcircuito. Disponibile nelle versioni 3V e 5V, M41ST87 integra molte funzioni diverse e utilizza l'alimentazione di backup da una batteria esterna o si trova normalmente nei sistemi, risparmiando anche sui costi. Il circuito di rilevamento delle intrusioni ha due ingressi indipendenti, ognuno dei quali può essere configurato per diversi schemi di connessione. Al rilevamento del fenomeno di manomissione, le opzioni dell'utente includono la cancellazione dei 128 byte interni di RAM, l'invio di un'interruzione al microprocessore di sistema e un pin di segnale dedicato per cancellare la RAM esterna. Queste funzionalità impediscono a un intruso di accedere ai dati sensibili (ad esempio, la password di un utente) contenuti in qualsiasi RAM, nonché di interrompere il processore di sistema per essere informato di una violazione della sicurezza. Queste funzioni sono fornite anche quando i chip M41ST87 funzionano in modalità con batteria tampone. Altre opzioni di sicurezza includono il rilevamento dei guasti dell'orologio e il timestamp automatico quando viene rilevata una manomissione. Inoltre, l'M41ST87 fornisce all'utente un numero di serie univoco a 64 bit. Anche il pacchetto di chip M41ST87 con quarzo incorporato contribuisce alla sicurezza. Oltre a risparmiare spazio e i costi associati alla manutenzione del sistema, il quarzo è chiuso dall'accesso esterno. Inoltre, è meglio protetto dagli effetti dell'ambiente naturale. Tenendo conto di tutti i fattori, si può sostenere che una tale soluzione di ST consente di ridurre il costo del sistema nel suo insieme. Supervisore chip NVRAM M41ST87 può essere utilizzato per gestire la RAM a basso consumo. Qui sono coinvolti i seguenti circuiti integrati: un circuito di commutazione automatica della batteria, un circuito di autorizzazione all'accesso (Chip - Enable Gate) per proteggere la RAM dalla scrittura e un monitor della batteria. Ciò consente all'utente di creare una NVRAM utilizzando la batteria di backup M41ST87 per alimentare la LPSRAM. L'M41ST87 si basa su un orologio in tempo reale programmabile alimentato a batteria con registri del contatore che traccia l'ora e la data con risoluzioni che vanno da centesimi di secondo a centinaia di anni. Sono accessibili tramite l'interfaccia I 2 C con una frequenza di 400 kHz. Formata utilizzando la tecnologia CMOS a bassa potenza, la RAM del circuito di clock in tempo reale M41ST87 è organizzata come 256x8 bit, con registri da 21 byte e dispone di 128 byte della propria NVRAM più 8 byte allocati a un numero di sequenza univoco. Il supervisore a microprocessore M41ST87 include due circuiti di pre-guasto alimentazione (PFI/PFO) indipendenti con un comparatore di riferimento a 1,25 V, un circuito di ripristino che può essere attivato da più sorgenti su due ingressi e un circuito di rilevamento interruzione alimentazione con uscita segnale. . Un timer watchdog con timeout programmabile da 62,5 ms a 128 sec può essere utilizzato anche come sorgente di ripristino. Inoltre, i circuiti di rilevamento manomissione possono essere configurati come fonti di ripristino. Uno o entrambi i circuiti PFI/PFO possono essere utilizzati non solo per il preavviso di un'interruzione di corrente, ma anche per controllare i circuiti di richiusura. Pertanto, è possibile monitorare fino a tre diverse tensioni di alimentazione (inclusa Vcc) utilizzando M41ST87. Il pacchetto SOX28 a basso profilo occupa poco spazio sulla scheda (2,4x10,42 mm inclusi i pin). I chip M41ST87 operano nell'intervallo di temperatura industriale da -40 o C a +85 o C. Per soluzioni a montaggio superficiale e RAM ad alta densità, ST suggerisce di utilizzare un supervisore separato e più LPSRAM. Una tale soluzione multi-chip spesso richiede meno spazio sulla scheda rispetto ad altre soluzioni ed è molto più economica rispetto ai DIP ibridi. Gli utenti possono collegare diverse quantità di LPSRAM al supervisore NVRAM ST appropriato, consentendo la configurazione di un'ampia varietà di densità e capacità. Le combinazioni tipiche includono: - Soluzione SMT 16Mbps, 3V o 5V con supervisore M40Z300 senza batteria superiore con quattro RAM a basso consumo tipo M68Z512; - Soluzione SMT 1Mbit o 4Mbit, 3V con supervisore SNAFAT® M40SZ100W e SRAM a bassa potenza tipo M68Z128W o M68Z512W. CI di serie POTENZA ZERO® prende il nome dalla capacità di salvare i dati in assenza di alimentazione di rete esterna. Sono costituiti da due componenti principali: RAM a basso consumo (LPSRAM) e NVRAM supervisore (Figura 4). La tipica LPSRAM consuma in genere meno di un µA quando funziona solo con la batteria e può conservare i dati per diversi anni se alimentata da una batteria al litio miniaturizzata. Il supervisore NVRAM è costituito da due circuiti principali: un circuito di commutazione della batteria e un circuito di protezione da scrittura. Il circuito di commutazione della batteria commuta l'alimentazione LPSRAM dall'alimentazione regolata dal sistema (Vcc) all'alimentazione della batteria (Vbat). Questo circuito monitora Vcc e quando inizia a diminuire, l'alimentazione alla LPSRAM viene trasferita alla batteria di backup.

Quando Vcc scende al di sotto di un certo valore di soglia, il microprocessore potrebbe comportarsi in modo irregolare e ciò potrebbe portare a scritture errate e persino a cancellare il contenuto della RAM. Il circuito di protezione da scrittura impedisce al microprocessore di accedere alla LPSRAM per prevenire questa situazione. Tutti i microcircuiti POTENZA ZERO® NVRAM Le aziende ST hanno le stesse capacità e non sono richiesti altri circuiti esterni. Attualmente vengono prodotti microcircuiti con supervisori NVRAM e LPSRAM integrati sullo stesso chip con densità fino a 256 kbit e inferiore. Per densità più elevate, vengono ancora utilizzati due microcircuiti separati.

I chip NVRAM della ST sono disponibili in una varietà di pacchetti. Il pacchetto base per montaggio superficiale (SMT) è il pacchetto SNAPHAT® (figura 5a). L'IC nel pacchetto SOH 28 ha una piedinatura SRAM standard e la batteria è fissata sulla parte superiore con elementi di fissaggio, il che ne facilita la sostituzione. Tipo di custodia BERRETTO (Fig. 5b) ha una batteria non rimovibile. È consigliato per applicazioni a foro passante. Per le soluzioni di montaggio a foro passante e l'elevata densità di RAM, viene offerto un pacchetto DIP ibrido, in cui LPSRAM e supervisore sono chip separati montati su un comune circuito stampato insieme a una batteria (Fig. 15c). Attualmente sono disponibili densità di RAM fino a 16 M bit. Pensando agli sviluppatori, una delle ultime NVRAM ZEROPOWER ® è il chip M 48 Z 32 V in un pacchetto a basso profilo. Patata fritta M48Z32V dispone di LPSRAM con una densità di memoria di 32 Kx8 a 3,3 V. Il pacchetto SOIC a 44 pin a basso profilo si erge di soli 0.12" (3,05 mm) sopra la scheda del circuito, offrendo agli utenti una maggiore flessibilità nel layout della scheda ed eliminando i problemi di spazio per i progettisti in altezza . chip M48Z32V dispone di un interruttore di backup della batteria integrato e circuiti di protezione da scrittura in caso di interruzione dell'alimentazione combinati con una SRAM a bassa potenza da 256 kbit. Il tempo di accesso per questi chip è di 35 ns per M48Z32V-35MT1 e 70 ns per M48Z32V-70MT1. Consumando solo 200 nA (tip. a 40°C), l'M48Z32V può memorizzare dati per dieci anni di durata della batteria con una capacità di 18 mAh. Questo chip è compatibile con i sistemi che già contengono batterie al litio sulla scheda. Combinando uno chassis di basso profilo con il valore M48Z32V consente di utilizzarlo come soluzione NVRAM di successo in molte applicazioni. Utilizzando i suoi contatti per connettersi a qualsiasi alimentazione a batteria, il chip M48Z32V può essere utilizzato come una normale RAM statica asincrona per qualsiasi microprocessore o microcontrollore. L'M48Z32V è prodotto in un pacchetto SO44, che è simile al pacchetto ST SOH44 SNPHAT®, ma senza la batteria superiore. È alimentato da un'alimentazione di 3,3 V (±10%) e funziona nell'intervallo di temperatura commerciale (da 0 a 70°C).

microchip TIMEKEEPER® NVRAM si basano sull'uso della tecnologia core NVRAM ST. Poiché i chip ZEROPOWER ® NVRAM sono alimentati a batteria, l'aggiunta di un orologio in tempo reale espande notevolmente le capacità e le applicazioni dei chip NVRAM. Il tuo nome TIMEKEEPER® tali microcircuiti sono stati ottenuti proprio per la presenza di un orologio in tempo reale con calendario, che fornisce al sistema l'ora, il giorno e la data esatti anche in assenza di alimentazione esterna del sistema (Fig. 6). I chip TIMEKEEPER® NVRAM sono basati su ZEROPOWER® NVRAM, a cui si aggiunge un circuito orologio/calendario in tempo reale, incluso un oscillatore a cristallo da 32 kHz. Il circuito di commutazione dell'alimentazione di emergenza utilizzato per memorizzare i dati in LPSRAM viene utilizzato anche per RTC. Allo stesso modo, nell'interesse della protezione in scrittura RTC, viene applicato lo schema di protezione in scrittura NVRAM. Il generatore RTC è ottimizzato per la potenza e il suo consumo non supera i 40 nA. Il principio di funzionamento dell'orologio in tempo reale consiste nell'utilizzare un oscillatore a 32 kHz, seguito dalla divisione di frequenza da diversi contatori. Il primo contatore divide la frequenza dell'oscillatore per 32,768 e produce un segnale con una frequenza di un hertz alla sua uscita. Il contatore successivo conta il numero di secondi e invia un segnale al contatore dei minuti una volta al minuto. I successivi contatori successivi continuano a dividere la frequenza verso il basso finché non viene emesso un impulso per secolo. Viene utilizzata una logica aggiuntiva per gestire il numero di giorni in ogni mese e tenere conto degli anni bisestili. I dati alle uscite dei contatori corrispondono all'ora e alla data correnti. Questi parametri vengono trasferiti all'area di memoria distribuita NVRAM e appaiono come indirizzi ordinari delle celle RAM. Gli utenti leggono/scrivono l'ora e la data leggendo/scrivendo questi indirizzi nello spazio NVRAM. I buffer forniscono la lettura/scrittura "senza soluzione di continuità" dei dati RTC. Durante la lettura dell'RTC, un frame di dati acquisiti sullo stato in tempo reale corrente viene archiviato nei buffer, da dove i dati vengono letti dal microprocessore. La presenza di un data frame garantisce l'invarianza del tempo durante il successivo ciclo di lettura da parte del microprocessore. Allo stesso modo, durante un ciclo di scrittura, i buffer conservano i dati provenienti dal microprocessore e attendono la fine del ciclo di scrittura delle informazioni giorno-data-ora per trasferire contemporaneamente i dati in ingresso ai contaore. I registri RTC sono mappati su LPSRAM. Per questo vengono utilizzati da 8 a 16 byte di LPSRAM. Il giorno, la data e l'ora vengono letti e scritti come normali indirizzi RAM. Incorporando ZEROPOWER ® NVRAM, i chip TIMEKEEPER ® NVRAM mantengono tutte le loro caratteristiche principali, inclusa l'assenza di circuiti esterni aggiuntivi. Con densità di memoria fino a 256 kbps, l'orologio in tempo reale e il supervisore NVRAM sono integrati sullo stesso die di LPSRAM. Per densità di memoria più elevate, viene utilizzato un chip LPSRAM separato. A seconda della tecnologia di esecuzione, i componenti che compongono il chip possono essere collocati in un unico package “ibrido”, oppure sullo stesso substrato in un package IC separato (la tecnologia emergente del packaging TIMEKEEPER®). Come i chip NVRAM TIMEKEEPER®, gli orologi seriali in tempo reale (Seriale CRT) traccia l'attuale tempo reale anche in assenza di alimentazione del sistema esterno. Invece dell'interfaccia parallela asincrona SRAM standard, gli RTC seriali utilizzano un bus seriale. I dispositivi ST sono disponibili in due versioni dell'interfaccia seriale standard del settore: I ? C e SPI. Questi chip si basano su TIMEKEEPER ® NVRAM riducendo la quantità di NVRAM a pochi byte e modificando l'interfaccia in uno degli standard sopra elencati. La maggior parte dei dispositivi Seriale RTC contengono un interruttore della batteria, circuiti di protezione da scrittura e molte altre moderne funzioni di supervisione del microprocessore, come il ripristino dell'alimentazione e il timer di watchdog (Fig. 7). Per le applicazioni che non richiedono ridondanza o richiedono solo una ridondanza a breve termine utilizzando un condensatore, ST fornisce dispositivi Serial RTC più semplici ed economici, come M 41 T 0 и M 41 T 80 .

I circuiti integrati di clock seriali in tempo reale con funzionalità complete ST hanno molte funzioni di supervisione del microprocessore. Per esempio, M 41 T81 - questo è RTC seriale con interfaccia I2C 400 kHz, Allarme, Watchdog programmabile, oscillatore ad onda quadra programmabile, in contenitore SO 8 o SOX28 SOIC (con quarzo incorporato). Patata fritta M 41 T 94 è il primo dispositivo Serial RTC ST con interfaccia SPI. Dispone di circuiti integrati P O R/LVD, Watchdog programmabile, Allarme, possibilità di collegare un pulsante di reset. Il chip è disponibile nelle confezioni SO 16 e SOH 28 SNPHAT ®. Chip seriale RTC M 41 ST 84 con interfaccia I2C 400 kHz si distingue per le avanzate capacità del supervisore a microprocessore. Oltre alle funzioni P O R / LVD, Watchdog e Allarme programmabili, fornisce una funzione di avviso di interruzione dell'alimentazione (PFI / PFO) e un reset dell'ingresso. Prodotto in custodia SO 16. I moderni chip ST NVRAM hanno raggiunto un tale livello di integrazione che alcuni di essi (M41ST85, M41ST87 и M41ST95) possono essere classificati sia come supervisori Serial RTC che TIMEKEEPER®. Il livello di integrazione raggiunto consente ora di posizionare il quarzo direttamente in un pacchetto di microcircuito monolitico accanto al cristallo e di non portarlo nella batteria superiore. Un esempio di tale soluzione che migliora l'affidabilità e la sicurezza è un microcircuito М41ST85МХ6 . Insieme a chip SERIAL RTC altamente integrati, ST produce dispositivi contenenti il minimo necessario per l'output continuo al sistema in tempo reale. I microchip sono tali dispositivi. M 41 T 0 и M 41 T80. Contengono un set completo di contatori del tempo e tengono conto delle peculiarità degli anni bisestili. Altre caratteristiche di questi dispositivi includono un allarme programmabile con gestione degli interrupt, un'uscita a onda quadra programmabile e un'uscita a 32kHz separata che può essere utilizzata come ingresso di riferimento per i generatori di clock su altri circuiti integrati. Con queste capacità, questi chip coprono le esigenze delle applicazioni in gran parte del mercato consumer. I circuiti integrati M41T0 e M41T80 dispongono di un'interfaccia seriale I standard del settore.2C 400 kHz e operano nell'intervallo di temperatura industriale da -40 o C a +85 o C. Prodotti in contenitori a montaggio superficiale, entrambi i dispositivi funzionano con un alimentatore con una tensione da 2 V a 5,5 V con basso consumo di corrente. Ad esempio, l'M41T0 assorbe solo 900 nA in modalità standby e 35 µA in modalità attiva (con un'alimentazione tipica di 3,0 V). L'M41T80 assorbe 1,5 µA in modalità standby (con un'alimentazione tipica di 3,0 V) e solo 30 µA in modalità attiva (con una tensione di alimentazione massima di 3,0 V). Oltre all'attività di temporizzazione di base, l'M41T0 dispone di un'opzione di bit di arresto dell'oscillatore per rilevare la deriva del clock dovuta a una riduzione della tensione di alimentazione. Per quanto riguarda l'M41T80, le sue funzioni di temporizzazione sono migliorate da un interrupt di allarme programmabile con modalità di ripetizione, un'uscita dedicata a 32kHz e un'uscita a onda quadra programmabile da 1Hz a 32kHz. L'uscita di frequenza dedicata a 32kHz può essere utilizzata per pilotare microprocessori e microcontrollori con un circuito di clock ad aggancio di fase che richiede 32kHz come riferimento. Inoltre, lo stesso pin può essere utilizzato per la sincronizzazione dell'orologio dei microcircuiti quando operano in modalità a basso consumo. L'uscita a 32 kHz è progettata per il funzionamento continuo, ma può essere disabilitata dal software dell'utente. La funzione di allarme del chip M41T80 ha una modalità di ripetizione dell'allarme da una volta all'anno a una volta al secondo. La funzione di programmazione dell'onda quadra consente di programmare la sua frequenza da 1 Hz a 32 kHz con un moltiplicatore di 2.

Il chip M41T80 si collega facilmente al bus I2C 400 kHz con quasi tutti i microprocessori e microcontrollori (Fig. 8) e, aggiungendo un diodo esterno e un condensatore, può sempre supportare il microcontrollore durante una momentanea interruzione di corrente. Poiché il pneumatico I2C funziona con scarico aperto, quindi non ci sono problemi di adattamento di tensione tra il microprocessore e l'M41T80, ed è sufficiente utilizzare un diodo per il disaccoppiamento della tensione. Quando si utilizza un condensatore da 1 F e una tensione di alimentazione Vcc di 3,3 V, il tempo di backup previsto è di circa 10 giorni. I circuiti integrati M41T80 sono disponibili in un contenitore SO8 di piccole dimensioni. Disponibile anche nel pacchetto TSSOP8. Il dispositivo più semplice della serie di chip SERIAL RTC ST è un chip M 41 T0, sviluppato sulla base di M41T00, M41T0. Questo dispositivo non ha un interruttore della batteria e una calibrazione dell'orologio software, ma ha una funzione di rilevamento dei guasti del generatore e un'interfaccia I2C da 400 kHz. chip M41T0 quando si utilizza un condensatore esterno da 1 F a 3,3 V, può fornire alimentazione di backup per un massimo di due settimane. La batteria superiore per i chip ST NVRAM viene fornita separatamente e questo deve essere tenuto in considerazione quando si ordinano questi circuiti. I chip di memoria NVRAM sono prodotti anche da altre società, ma molti di essi non hanno le stesse caratteristiche inerenti ai componenti ST. I chip NVRAM STMicroelectronics si distinguono principalmente per una maggiore integrazione, la presenza di un interruttore batteria integrato e la possibilità di calibrare programmaticamente l'orologio, per il quale viene utilizzato il software (disponibile sul sito Web ST). Pubblicazione: cxem.net

Pelle artificiale per l'emulazione del tocco

15.04.2024 Lettiera per gatti Petgugu Global

15.04.2024 L'attrattiva degli uomini premurosi

14.04.2024

▪ Smartphone fuoristrada V-Phone X3 con batteria da 4500 mAh ▪ La Terra ha un altro satellite

▪ sezione del sito Roba da spia. Selezione dell'articolo ▪ articolo Regole elementari delle riprese video. videoarte ▪ articolo Che tipo di dinosauri erano a sangue freddo oa sangue caldo? Risposta dettagliata ▪ articolo Insegnante di educazione fisica. Istruzioni standard sulla protezione del lavoro ▪ articolo Palla tra le dita. Messa a fuoco segreta

Homepage | Biblioteca | Articoli | Mappa del sito | Recensioni del sito www.diagram.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

Lascia il tuo commento su questo articolo:

Lascia il tuo commento su questo articolo: