|

|

ENCICLOPEDIA DELLA RADIOELETTRONICA ED ELETTRICA Bus di controllo I2C. Enciclopedia della radioelettronica e dell'ingegneria elettrica

Enciclopedia della radioelettronica e dell'elettrotecnica / Компьютеры I2C è un'interfaccia a due fili sviluppata da Philips. La specifica originale per l'interfaccia aveva una velocità dati massima di 100 Kbps. Tuttavia, nel tempo, sono comparsi degli standard per modalità operative più veloci I2C. Ad una gomma I2C, è possibile collegare dispositivi con velocità di accesso diverse, poiché la velocità dati è determinata dal segnale di clock. Il protocollo di trasferimento dei dati è progettato in modo tale da garantire una ricezione affidabile dei dati trasmessi. Durante il trasferimento dei dati, un dispositivo è il “Master”, che avvia il trasferimento dei dati e genera segnali di sincronizzazione. Un altro dispositivo "Slave" - inizia la trasmissione solo su comando proveniente dal "Master". I microcontrollori PIC16CXXX implementano nell'hardware la modalità “Slave” del dispositivo nel modulo SSP. La modalità "Master" è implementata nel software. Termini di base usati per descrivere il funzionamento del bus I2C: Trasmettitore - un dispositivo che trasmette dati su un bus ricevitore - un dispositivo che riceve i dati dal bus "Maestro" - un dispositivo che avvia la trasmissione e genera un segnale di clock "schiavo" - il dispositivo a cui accede il "Master" Multi "Maestro" - modalità bus I2C con più di un "Master" Arbitrato - procedura per garantire che un solo "Master" controlli il bus sincronizzazione - procedura per sincronizzare il segnale di clock da due o più dispositivi Gli stadi di uscita dei generatori di segnali di sincronizzazione (SCL) e dati (SDA) devono essere realizzati secondo circuiti open-collector (drain) per combinare più uscite e collegati tramite un resistore esterno al positivo di alimentazione in modo che il livello del bus sia “ 1” quando nessuno dei due dispositivi genera un segnale "0". Il carico capacitivo massimo è limitato a 400 pF di capacità. Inizializzazione e completamento del trasferimento dei dati Quando non c'è trasferimento di dati sul bus, i segnali SCL e SDA sono alti a causa di una resistenza esterna. I segnali di START e STOP sono generati dal "Master" per determinare rispettivamente l'inizio e la fine del trasferimento dei dati. Il segnale START è generato da una transizione da alto a basso del segnale SDA mentre il segnale SCL è alto. Il segnale STOP è definito come la transizione SDA da basso ad alto quando SCL è alto. Pertanto, durante la trasmissione di dati, il segnale SDA può cambiare solo quando il segnale SCL è basso.

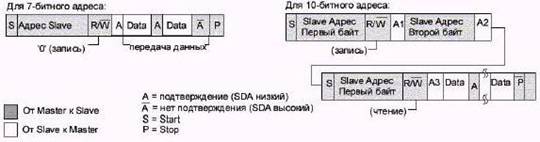

Indirizzamento del dispositivo sul bus I2C Per indirizzare i dispositivi vengono utilizzati due formati di indirizzo: Semplice formato a 7 bit con bit di lettura/scrittura R/W;

e formato a 10 bit - nel primo byte vengono trasmessi i due bit più significativi dell'indirizzo e il bit di scrittura/lettura, nel secondo byte viene trasmessa la parte bassa dell'indirizzo.

Conferma di accettazione Durante la trasmissione dei dati, dopo ogni byte trasmesso, il ricevitore deve confermare la ricezione del byte con un segnale ACK. Se lo "Slave" non conferma la ricezione dell'indirizzo o del byte di dati, il "Master" deve interrompere la trasmissione generando un segnale STOP. Quando si trasmettono dati da "Slave" a "Master", "Master" genera segnali di riconoscimento dei dati ACK. Se il "Master" non conferma la ricezione del byte, lo "Slave" interrompe la trasmissione dei dati "rilasciando" la linea SDA. Successivamente il "Master" può generare un segnale di STOP. Per ritardare la trasmissione dei dati, lo "Slave" può impostare uno zero logico, indicando al "Master" di attendere. Dopo che la linea SCL viene rilasciata, il trasferimento dei dati continua.

Trasferimento dati da "Master" a "Slave"

Lettura dei dati da "Slave"

Utilizzo del segnale di Re-START per accedere allo "Slave"

Modalità multimaster Protocollo di comunicazione I2C consente di avere più di un "Master" sul bus. Le funzioni di arbitraggio e sincronizzazione vengono utilizzate per risolvere i conflitti del bus durante l'inizializzazione della trasmissione. Arbitrato L'arbitrato viene eseguito sulla linea SDA quando la linea SCL è alta. Un dispositivo che genera un livello alto sulla linea SDA quando un altro trasmette basso perde il diritto di prendere il “Master” e deve passare alla modalità “Slave”. Un “Master” che ha perso l'iniziativa sul bus può generare impulsi di clock fino alla fine del byte in cui ha perso le sue proprietà di master.

sincronizzazione L'orologio sul bus si verifica dopo che l'arbitrato è stato eseguito sul segnale SCL. Quando il segnale SCL passa da alto a basso, tutti i dispositivi interessati iniziano a contare la durata del livello basso. I dispositivi iniziano quindi a passare da SCL basso ad alto in base alla velocità dati richiesta. Dopo che il livello passa da basso a alto, i dispositivi interessati contano la durata del livello alto. Il primo dispositivo che abbassa il segnale SCL determina i parametri di clock.

Pubblicazione: cxem.net

Un nuovo modo di controllare e manipolare i segnali ottici

05.05.2024 Tastiera Seneca Premium

05.05.2024 Inaugurato l'osservatorio astronomico più alto del mondo

04.05.2024

▪ Un nuovo metodo per convertire l'anidride carbonica in metano ▪ NCP694 - Regolatore LDO da 1 amp di ONSemi ▪ Pacemaker che funziona dal cuore

▪ sezione del sito Messa a terra e messa a terra. Selezione di articoli ▪ articolo Giardino fiorito su ruote. Suggerimenti per il padrone di casa ▪ Perché alcune persone soffrono di allergie e altre no? Risposta dettagliata ▪ articolo Magliaia di prodotti tessili e merceria. Istruzioni standard sulla protezione del lavoro ▪ articolo Fiori di sapone. esperimento fisico

Homepage | Biblioteca | Articoli | Mappa del sito | Recensioni del sito www.diagram.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

Lascia il tuo commento su questo articolo:

Lascia il tuo commento su questo articolo: